Analysis Of Combination Logic Circuit

Analysis Of Combination Logic Circuit

The function of an existing combination logic circuit is expressed by the Boolean equation that describes the signal that appears at its output terminal(s). The output function can be determined by following through the circuit the output of each gate as it is connected to the inputs of one or more other gates.

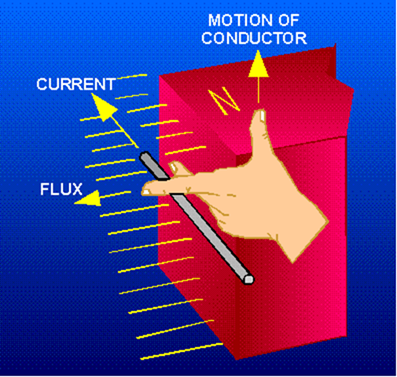

An example of this is given by the circuit shown in Fig. 20. The output of the upper NAND gate is AB and the output of the lower AND gate is EC. These two outputs are applied to the input of the OR gate. Hence, the output of the circuit is F = AB + BC. The truth table of the circuit is given by Table 14.Table 14 .

A rather more complex circuit is shown in Fig .12. The upper NAND gate has Ā and B as its inputs and so its output is . Similarly, the output of the lower NAND gate is

. These two outputs are applied to the inputs of the third NAND gate. The output of the circuit is

If the last line of the table is compared with the last line of Table 8.8 it will be seen that they are identical. This means that the circuit given in Fig. 21 performs the logical function exclusive-OR.