Application-Specific Integrated Circuits

Introduction

Application specific integrated circuits (ASICs), also called custom ICs, are chips specially designed to (1) perform a function that cannot be done using standard components, (2) improve the performance of a circuit, or (3) reduce the volume, weight, and power requirement and increase the reliability of a given system by integrating a large number of functions on a single chip or a small number of chips.

ASICs can be classified into the following three categories: (1) full custom, (2) semicustom, and (3) programmable logic devices (PLDs).

The first step of the process toward realizing a custom IC chip is to define the function the chip must perform. This is accomplished during system partitioning, at which time the system engineers and IC designers make some initial decisions as to which circuit functions will be implemented using standard, off the shelf, components and which will require custom ICs. After several iterations the functions that each custom chip has to perform are determined.

There usually are many different ways by which a given function may be implemented. For example, the function may be performed in either the analog or the digital domain. If a digital approach is selected, different execution strategies may be chosen. For example, a delay function may be implemented either by a shift register or by a random access memory. Thus, in the second step of the process, the system engineers and IC designers decide how the functions each of the chips has to perform will be executed. How a function is executed by a given chip constitutes the behavioral description of that chip.

Next, a design approach needs to be developed for each of the custom chips. Depending on the implementation method selected, either a full custom, a semicustom, or a user programmable device approach is chosen.

One important consideration in the design choice is cost and turn around time(Fey and Paraskevopoulos, 1985). Typically, a full custom approach takes the longest to design, and the cost per chip is very high unless the chip volume is also high, normally more than a few hundred thousands chips per year. The shortest

design approach is using programmable devices but the cost per chip is the highest. This approach is best for prototype and limited production systems.

In a typical full custom IC design, every device and circuit element on the chip is designed for that particular chip. Of course, common sense dictates that device and circuit elements proven to work well in previous designs are reused in subsequent ones whenever possible.

A full custom approach is selected to minimize the chip size or to implement a function that is not available or would not be optimum with semicustom or standard ICs. Minimizing chip size increases the fabrication yield and the number of chips per wafer. Both of these factors tend to reduce the cost per chip.

Fabrication yield is given by

where A is the chip or die area and D is the average number of defects per square centimeter per wafer. The number of die per wafer is given by

where R is the wafer radius and A is, again, the area of the die.

Additional costs incurred involve testing of the die while still on the wafer and packaging a number of the good ones and testing them again. Then good die must be subjected to reliability testing to find out the expected lifetime of the chip at normal operating conditions (Hu, 1992).

Fabrication of full custom ASICs is done at silicon foundries. Some of the foundries are captive, that is, they fabricate devices only for the system divisions of their own company. Others make available some of their lines to outside customers. There also are foundries that exclusively serve external customers.

Foundries often provide design services as well. If users are interested in doing their own design, however, then the foundry provides a set of design rules for each of the processes they have available. The design rules describe in broad terms the fabrication technology, whether CMOS, bipolar, BiCMOS, or GaAs and then specify in detail the minimum dimensions that can be defined on the wafer for the various layers, the SPICE [Vladimirescu et al. 1981] parameters of each of the active devices, the range of values for the passive devices and other rules and limitations.

Designing a full custom chip is a complex task and can only be done by expert IC designers. Often a team of people is required both to reduce the design time (Fey and Paraskevopoulos, 1986) and because one person may simply not have all the design expertise required. Also, sophisticated and powerful computer hardware and software are needed. Typically, the more sophisticated the computer aided design (CAD) tools are, the higher the probability that the chip will work the first time. Given the long design and fabrication cycle for a full custom chip and its high cost, it is important that as much as possible of the design be automated, that design rule checking should be utilized, and that the circuit simulation be as complete and accurate as possible.

During the design phase, a substantial effort should be made to incorporate on the chip additional circuitry to help verify that the chip is working properly after it is fabricated, or to help identify the section or small circuit responsible for the chip not working, or verify that an error occurred during the fabrication process. For digital full custom circuits, a large number of testability techniques have been developed (Williams and Mercer, 1993), most of which are automated and easily incorporated in the design, given the proper software. For analog circuits there are no accepted universal testability methods.

A unique test methodology for each circuit needs to be developed.

Technology selection for a particular full custom ASIC depends on the functions the chip has to perform, the performance specifications, and its desired cost.

The main distinguishing feature of semicustom ASICs, compared to full custom ones, is that the basic circuit building blocks, whether analog or digital, are already designed and proven to work. These basic circuits typically reside in libraries within a CAD system. The users simply select from the library the components needed, place them on their circuits, and interconnect them. Circuit simulation is also done at a much higher level than SPICE, and the designer is, therefore, not required to be familiar with either semiconductor or device physics.

Semicustom ICs are designed using either gate arrays, standard cells, analog arrays, functional blocks and PLDs such as field programmable gate arrays (FPGAs). Note that there does not exist a standard naming convention for these products within the industry. Often different manufacturers use different names to describe what are essentially very similar products. Gate arrays, standard cells, and FPGAs are used for digital designs. Analog arrays are used for analog designs and functional blocks are used for both.

A gate array consists of a regular array of transistors, usually arranged in two pairs of n- and p-channel, which is the minimum number required to form a NAND gate, and a fixed number of bonding pads, each incorporating an input/output (I/O) buffer. The major distinguishing feature of gate arrays is that they are partially prefabricated by the manufacturer. The designer customizes only the final contact and metal layers. Partially prefabricating the devices reduces delivery time and cost, particularly of prototype parts. The layout of a simple 2048-gates CMOS gate array is shown in Fig. 11.1. The device consists of 16 columns of transistors and each column contains 128 pairs of n-channel and p-channel transistors. Between the columns are 18 vertical wiring channels, each containing 21 tracks. There are no active devices in the channels. There are 4 horizontal wiring tracks for each gate for a total of 512 horizontal tracks or routes for the whole array. The optimum number R of wiring tracks or routes per gate, of an array of a given number of gates, is given by the empirical formula (Fier and Heikkila, 1982)

Where C is the average number of connections per gate and G is the number of gates in the array. For a two-input NAND gate, shown in Fig. 11.2, the number of connections C is 3, the two inputs A and B and the output AB , and for a 2048-gates array, the preceding formula gives R = 23. In this device 25 routes per gate are provided.

In the perimeter of the device 68 bond pads are arranged. Of these, 8 pads are needed for power and ground connections. Another empirical formula (Fier and Heikkila, 1982), based on Rent’s rule, specifies that the number of I/O pads required to communicate effectively with the internal gates is given by

where P is the sum of input and output pads, C is again the number of connections per gate, G is the number of gates in the array and a is Rent’s exponent having a value between 0.5 and 0.7. For large-scale integrated (LSI) circuits, typically a = 0.46. Assuming this value for a, then P is equal to 134 for G = 2048 and C = 3. This gate array, therefore, with only 60 I/O pads should be pad limited for many designs.

As mentioned previously, the process of designing with gate arrays begins with the designer drawing, with the aid of a CAD system, the circuit schematic representing the function the chip must perform. This activity is called schematic capture. The schematic, containing circuit elements or cells, such as inverters, NAND and NOR gates, flip-flops, adders, etc., is formed by getting these components from a specified

library in the computer. Each of the cells has a number of representations associated with it. It has a schematic used, of course, in drawing up the complete circuit schematic. It has a functional description that specifies what the element does, for example, an inverter takes an 1 input and produces a 0 in its output and vice versa. Another file describes its electrical characteristics, such as the time delay between when the inputs reach a certain state and the time the output responds to that state, often referred to as the propagation delay, and it has a physical representation.

In the array shown in Fig. 11.1, before the customized layers are placed on the device, each of the 2048 gates appears schematically as shown in Fig. 11.3. There are two n-channel transistors on the left and two p-channel transistors on the right. There is also a ground or VSS buss line running vertically on the left and a VDD line on the right. Figure 11.4 shows the equivalent electrical schematic of the structure in Fig. 11.3. In Fig. 11.5 is shown only one pair of n- and p-channel transistors and locations within the device area where one of the customizing layers, the contacts, may be placed. The physical representation of a particular library cell contains information of how the uncommitted transistors in the device columns should be connected.

As an example, in Fig. 11.6 is shown a portion of one of the 16 device columns in the array. Figure 11.7 shows the location of the contact holes, shown as white squares, and the metal interconnects, for an inverter shown as the dark horizontal bars. An actual inverter circuit is realized by placing this inverter cell along anywhere in the column, as shown in Fig. 11.8. Figure 11.9 shows the electrical connections made in the gate array and in Fig. 11.9(b) is shown, for reference, the electric schematic for an inverter. Note that in Fig. 11.8 and Fig. 11.9, the polysilicon gates of the top and bottom n-channel transistors are connected to VSS and the corresponding gates of the the p-channel transistors are connected to VDD. This is done to isolate the inverter from interfering electrically with another logic gate that may be placed above or below it. Returning to the design process, after schematic capture is completed, the designer simulates the entire circuit first to verify that it performs the logic functions the circuit is designed to perform and then using the electrical specifications files, a timing simulation is performed to make sure the circuit will operate at the clock frequency desired. However, the timing simulation is not yet complete. In the electrical characteristics file of each cell, a typical input and load capacitance is assumed. In an actual circuit the load capacitance may be quite different. Therefore, another timing simulation must be done after the actual capacitance values are found for each node.

To do this, first from the circuit schematic, a netlist is extracted. This list contains exact information about which node of a given element is connected to which nodes of other elements. This netlist is then submitted to the place and route program. This program places all of the elements or cells in the circuit on the gate array, in a fashion similar to what was done in Fig. 11.8, and attempts to connect them as specified in the netlist. The program may iterate the placement of cells and interconnection or routing until all cells listed in the netlist are placed on the gate array and interconnected as specified.

Once the circuit is placed and routed, an extraction program is applied that does two things. First, it calculates the actual resistance and capacitance seen at each node of the circuit that is then fed back into the netlist for more accurate timing simulation; second, it extracts a new netlist of the circuit on the gate array that can be compared with the initial netlist. The two netlists should, of course, be identical. However, often manual intervention is required to finish either the placement or routing of a particularly difficult circuit and that could cause an inadvertent error to occur in the layout. The error is then detected by comparing this extracted netlist to the original one.

The input test vector is not, typically, similar to what the chip will see in actual operation. Instead, the goal is to select a set of input vectors that when applied to the chip will cause every internal node to change state at least once. The timing verification program is used for this task. The program keeps track of the nodes toggled, as each input vector is applied, and also saves the output vector. When the finished devices are received, the same input test vectors are applied in sequence, and the resulting output vectors are captured and compared to those obtained from the timing simulation runs. If the two match perfectly, the device is classified as good.

The purpose of this test is to detect whether, because of a defect during fabrication, an internal gate is not operating properly. Usually if a test can cause about 90% of the internal nodes to switch state, it is considered to provide adequate coverage. It would be desirable to have 100% coverage, but often this is not practical because of the length of time it would take for the test to be completed. Finally, because the test is done at the frequency at which the chip will operate, only minimal functional testing is performed.

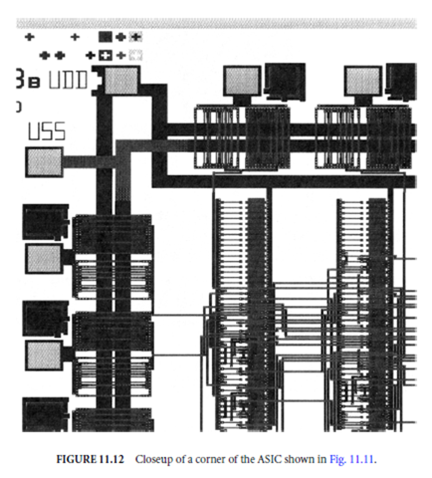

Just as in the device columns any logic gate can be placed anywhere in any of the columns, each of the pads can serve as either an input, an output, or a power pad, again by customizing the four layers. Figure 11.13 shows an I/O buffer at the end of the prefabrication process. Figure 11.14 shows the contact and metal pattern to make the uncommitted pad an inverting output buffer and Fig. 11.15 shows the two

The gate array architecture presented here is not the only one. A number of different designs have been developed and are currently used. For each of the architectures, a different place and route algorithm is then developed to take advantage of that particular design. Gate arrays have also taken advantage of developments in silicon technology, which primarily consists of shrinking of the minimum dimensions. As a result, arrays with several million transistors per chip are presently in use.

Designing with gate arrays is fairly straightforward and is utilized extensively by system engineers. However, gate arrays are quite inefficient in silicon area use since the number of transistors, the number of routing tracks, and the number of I/O pads needed by a particular circuit does not always match the number of devices or pads on the array, which are, of course, fixed in number.

The standard cells design methodology was developed to address this problem. As was the case for gate arrays, a predesigned and characterized library of cells exists for the circuit designer to use. But, unlike gate arrays, the chip is layed out containing only the number of transistors and I/O pads specified by the particular circuit, resulting in a smaller, less expensive chip. Fabrication of a standard cells circuit, however, must start from the beginning of the process. This has two major drawbacks. First, the fabrication time for standard cells is several weeks longer than for gate arrays; second, the customer has to pay for the fabrication of the whole lot of wafers, whereas for gate arrays, only a small portion of the lot is processed for each customer. This substantially increases the cost of prototype parts.

Advances in place and route software have made possible the functional blocks design methodology. Here the cells are no longer simple logic gates, but complete functions. The cells can be analog or digital and can have arbitrary sizes. Figure 11.20 shows an example of a digital functional block design. In the figure, the three white blocks are placed and routed automatically along with several rows of standard cells. In Fig. 11.21, a small linear charge-coupled device (CCD) image sensor, located in the center of the chip, and a few other analog circuits, located below it, are placed on the same chip with a block of standard cells that C produce all of the logic needed to run the chip. In this chip, care is taken as to both the placement of the various blocks and the routing because of the sensitivity of the analog circuits to noise, temperature, and other factors. Therefore, the designer had considerable input as to the placement of the various blocks and the routing, and the software is designed to allow this intervention, when needed.

Often the digital functional blocks are built by a class of software programs called silicon compilers or synthesis tools. With such tools circuit designers typically describe the functionality of their circuit at the behavioral level rather than the gate level, using specially developed computer languages called hardware description languages (HDL). These tools can quickly build memory blocks of arbitrary size, adders or multipliers of any length, PLAs, and many other circuits.

It should be obvious by now that the semicustom design approach makes heavy use of software tools. These tools eliminate the tedious and error prone task of hand layout, provide accurate circuit simulation, and help with issues such as testability. Their power and sophistication make transparent the complexity inherent in the design of integrated circuits.

Analog Arrays

Analog arrays are typically made in a bipolar process and are intended for the fabrication of high- performance analog circuits. Like gate arrays, these devices are prefabricated up to the contact level and, like all semicustom approaches, they are provided with a predesigned and characterized cell library. Because of the infinite variety of analog circuits, however, designers often design many of their own cells

The architecture of analog arrays is tile like, as shown in Fig. 11.22. Each tile is identical to all other tiles. Within each tile is contained a number of transistors, resistors, and capacitors of various sizes. The array also contains a fixed number of I/O pads, each of which can be customized with the last four layers to serve either as an input or output buffer. Figure 11.23 shows an actual circuit (Boisvert and Gaboury, 1992) implemented in a commercially available analog array.

ASICs: The acronym of application specific integrated circuits; another name for such chips is custom integrated circuits.

Functional blocks: ASICs designed using this methodology are more compact than either gate arrays or standard cells because the blocks can perform much more complex functions than do simple logic gates.

Gate arrays: Chips that contain uncommitted arrays of transistors and are prefabricated up to a certain step after which they are customized for the particular application.

Nonreccurring engineering (NRE): Costs the foundry charges the ASIC customer. These costs include engineering time, the cost of making the masks, the cost of fabricating one lot of wafers, and for packaging and testing the prototype parts.

Standard cells: A design methodology for realizing ASICs. Compared to gate arrays, they make more efficient use of silicon.

Schematic capture: The process by which the functionality of the chip is captured in an electrical schematic, usually with the aid of a computer, and using components from a cell library resident in that computer.

Silicon compilers, synthesis tools: Software programs that can construct an ASIC whose functionality is no longer described by a circuit schematic but in a special high level computer languages, generally called hardware description languages or HDL.

Test vectors: A test scheme that consists of pairs of input and output. Each input vector is a unique set of 1s and 0s applied to the chip inputs and the corresponding output vector is the set of 1s and 0s produced at each of the chip’s output.

Boisvert, D.M. and Gaboury, M.J. 1992. An 8–10-bit, 1–40 MHz analog signal processor with configurable performance for electronic imaging applications. In Proceedings IEEE International ASIC Conference and Exhibit, pp. 396–400. Rochester, NY.

Fey, C.F. and Paraskevopoulos, D. 1985. Selection of cost effective LSI design methodologies. In Proceedings of the IEEE Custom Integrated Circuits Conference, pp. 148–153. Portland, OR.

Fey, C.F. and Paraskevopoulos, D. 1986. A model of design schedules for application specific ICs. In

Proceedings IEEE Custom Integrated Circuits Conference, pp. 490–496. Rochester, NY.

Fier, D.F. and Heikkila, W.W. 1982. High performance CMOS design methodologies. In Proceedings IEEE

Custom Integrated Circuits Conference, pp. 325–328. Rochester, NY.

Hu, C. 1992. IC reliability simulation. IEEE J. of Solid State Circuits 27(3):241–246; see also Proceedings of

the Annual International Reliability Physics Symposium.

Ting, G., Guidash, R.M., Lee, P.P.K., and Anagnostopoulos, C. 1994. A low-cost, smart-power BiCMOS

driver chip for medium power applications. In Proceedings IEEE International ASIC Conference and

Exhibit, pp. 466–469. Rochester, NY.

Vladimirescu, A. et al. 1981. SPICE Manual. Dept. of Electrical Engineering and Computer Sciences,

University of California, Berkeley, CA, Oct.

Williams, T.W. and Mercer, M.R. 1993. Testing digital circuits and design for testability. In Proceedings IEEE International ASIC Conference and Exhibit (Tutorial Session), p. 10. Rochester, NY.

The ASIC field has been expanding rapidly since about 1980. The best source of current information is the two major conferences where the more recent technology developments are reported. These are the IEEE Custom Integrated Circuits Conference (CICC) held annually in May and the IEEE International ASIC Conference and Exhibit, held annually in September. IEEE Spectrum Magazine lists these conferences in the calender of events. Apart from the regular technical sessions, educational sessions and exhibits by ASIC vendors are part of these two conferences.

An additional resource is the USC/Information Sciences Institute, 4676 Admiralty Way, Marina del Rey, CA 90292-6695, Telephone (213) 822-1511.

Finally, a selected number of papers from the CICC are published every year, since 1984, in special issues of the IEEE Journal of Solid State Circuits.

Additional information can also be found in a number of other conferences and their proceedings, including the Design Automation Conference (DAC) and the International Solid States Circuits Conference (ISSCC).